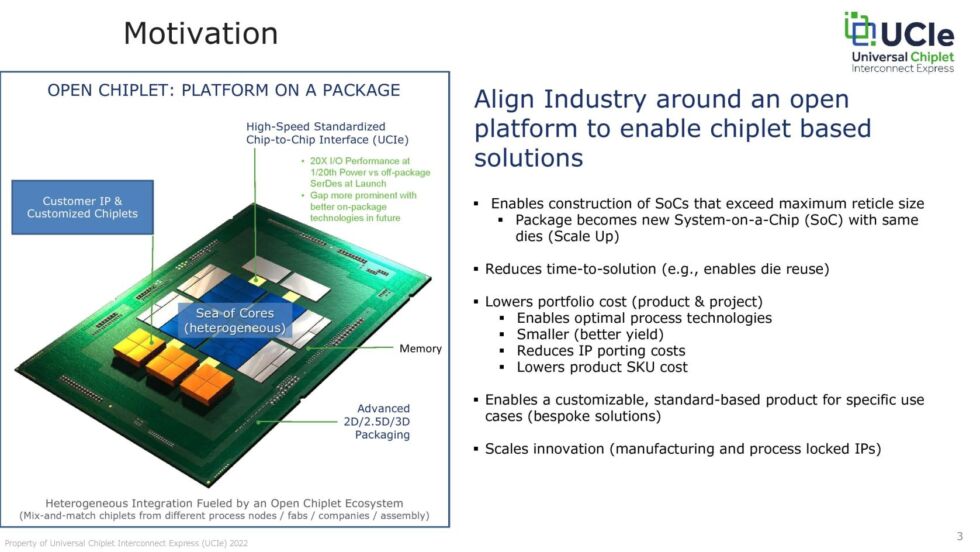

Enlarge / A sample chiplet design, with the CPU dies made with a more advanced manufacturing process and the chipset and some other functions made on older, cheaper processes. (credit: Universal Chipset Interconnect Express)

Some of the CPU industry's heaviest hitters—including Intel, AMD, Qualcomm, Arm, TSMC, and Samsung—are banding together to define a new standard for chiplet-based processor designs. Dubbed Universal Chiplet Interconnect Express (UCIe for short), the new standard seeks to define an open, interoperable standard for combining multiple silicon dies (or chiplets) into a single package.

Intel, AMD, and others are already designing or selling chiplet-based processors in some form—most of AMD's Ryzen CPUs use chiplets, and Intel's upcoming Sapphire Rapids Xeon processors will, too. But these chips all use different interconnects to enable communication between chiplets. The UCIe standard, if it succeeds, will replace those with a single standard, in theory making it much easier for smaller companies to take advantage of chiplet-based designs or for one company to include another company's silicon in its own products.

-

The UCIe (which is the name of the specification and the organization) lays out its goals in defining the UCIe standard. [credit: Universal Chipset Interconnect Express ]

Chiplet-based designs are advantageous when making large chips on cutting-edge manufacturing nodes partly because they cut down on the amount of silicon manufacturers need to throw out. If a manufacturing defect affects one CPU core, tossing (or binning) a single 8-core chiplet is a whole lot cheaper than having to toss a huge 16- or 32-core processor die. Chiplet designs also let you mix-and-match chips and manufacturing processes. You could, for example, use an older, cheaper process for your chipset and a newer, cutting-edge process for your processor cores and cache. Or you could put an AMD GPU on the same package as an Intel CPU.

Read 4 remaining paragraphs | Comments

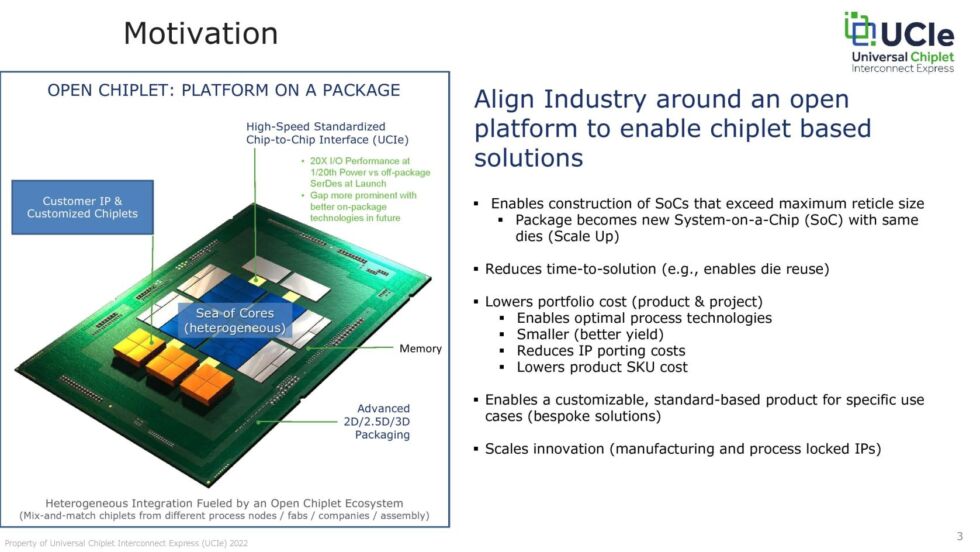

Enlarge / A sample chiplet design, with the CPU dies made with a more advanced manufacturing process and the chipset and some other functions made on older, cheaper processes. (credit: Universal Chipset Interconnect Express)

Some of the CPU industry's heaviest hitters—including Intel, AMD, Qualcomm, Arm, TSMC, and Samsung—are banding together to define a new standard for chiplet-based processor designs. Dubbed Universal Chiplet Interconnect Express (UCIe for short), the new standard seeks to define an open, interoperable standard for combining multiple silicon dies (or chiplets) into a single package.

Intel, AMD, and others are already designing or selling chiplet-based processors in some form—most of AMD's Ryzen CPUs use chiplets, and Intel's upcoming Sapphire Rapids Xeon processors will, too. But these chips all use different interconnects to enable communication between chiplets. The UCIe standard, if it succeeds, will replace those with a single standard, in theory making it much easier for smaller companies to take advantage of chiplet-based designs or for one company to include another company's silicon in its own products.

-

The UCIe (which is the name of the specification and the organization) lays out its goals in defining the UCIe standard. [credit: Universal Chipset Interconnect Express ]

Chiplet-based designs are advantageous when making large chips on cutting-edge manufacturing nodes partly because they cut down on the amount of silicon manufacturers need to throw out. If a manufacturing defect affects one CPU core, tossing (or binning) a single 8-core chiplet is a whole lot cheaper than having to toss a huge 16- or 32-core processor die. Chiplet designs also let you mix-and-match chips and manufacturing processes. You could, for example, use an older, cheaper process for your chipset and a newer, cutting-edge process for your processor cores and cache. Or you could put an AMD GPU on the same package as an Intel CPU.

Read 4 remaining paragraphs | Comments

March 03, 2022 at 02:26AM

Post a Comment